Simulink HDL |

您所在的位置:网站首页 › simulink 滤波模块 › Simulink HDL |

Simulink HDL

|

Simulink HDL

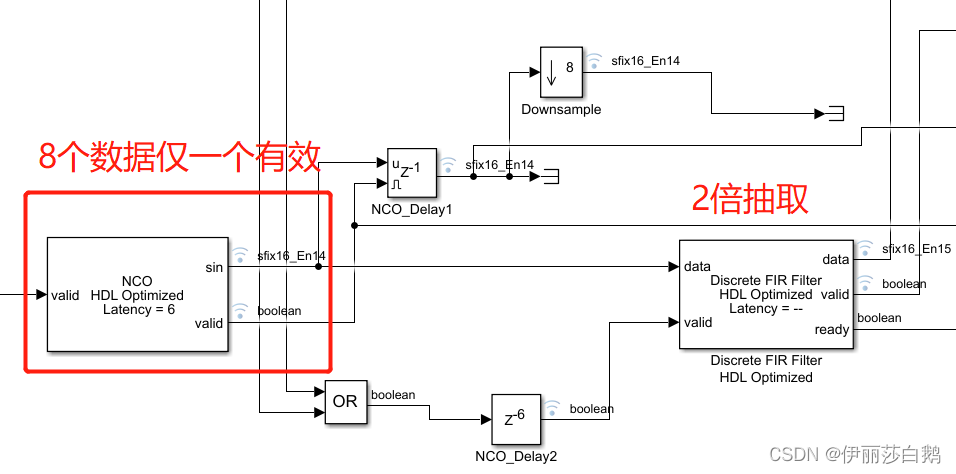

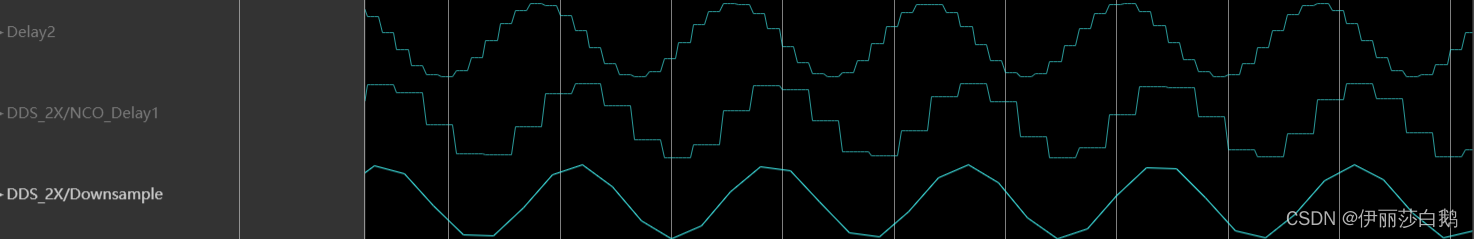

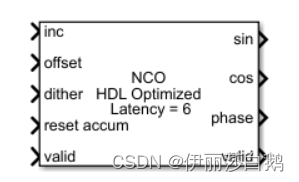

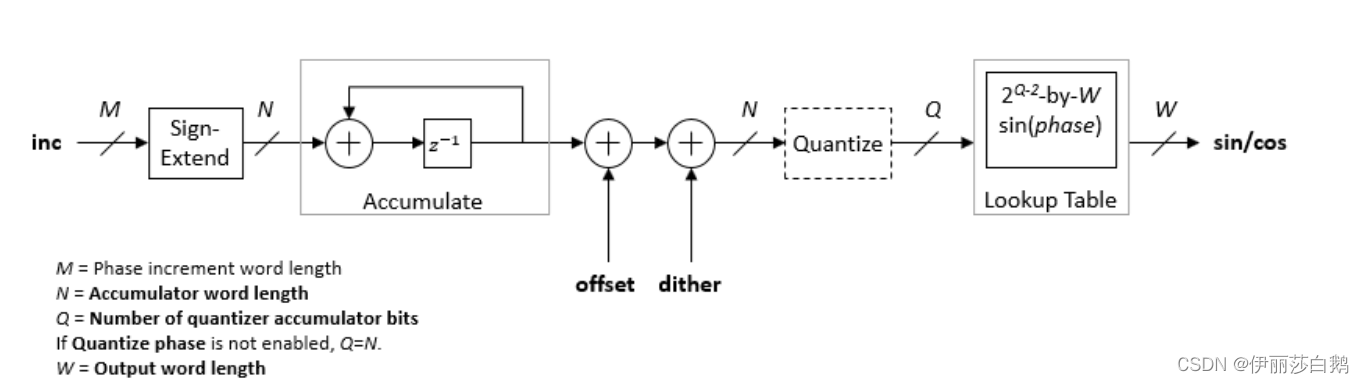

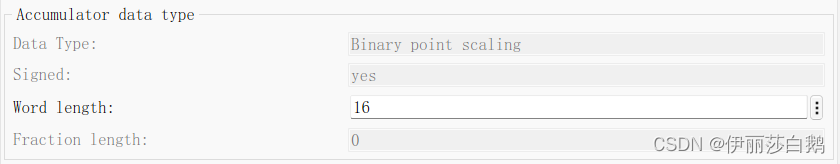

Simulink生成HDL的方法可以快速设计出工程,并结合FPGA验证,相比于手写HDL代码优化不足。该方法适合做工程的快速验证和基本框架搭建,是学习系统化FPGA设计的一种方法。 本次实验要点:多周期DDS,每8个周期出一个有效值样点。整个电路使用同一个时钟驱动。 实验模块: NCO HDL Optimized & Discrete FIR Filter HDL Optimized 参考文章 Matlab 的帮助文档 一、NCO HDL OptimizedMatlab帮助文档的模块描述:NCO HDL优化块生成实或复正弦信号,同时提供适应硬件的控制信号。数控振荡器(NCO)累积相位增量,并使用累加器的量化输出作为包含正弦波值的查找表的索引。定点累加器和量化器数据类型的环绕提供了正弦波的周期性,量化减少了给定频率分辨率所需的表的大小。 模块接口

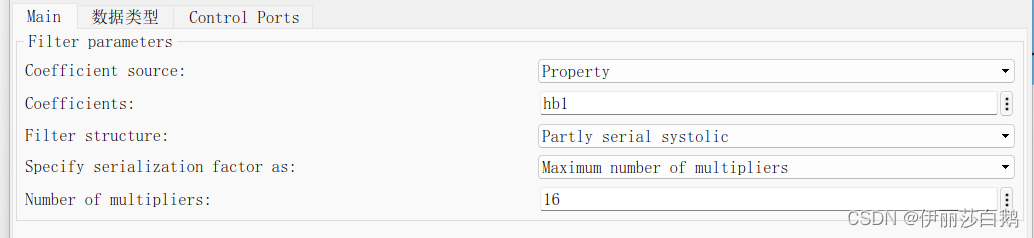

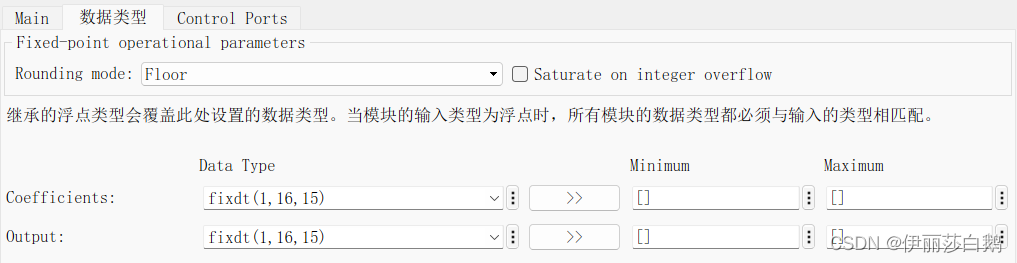

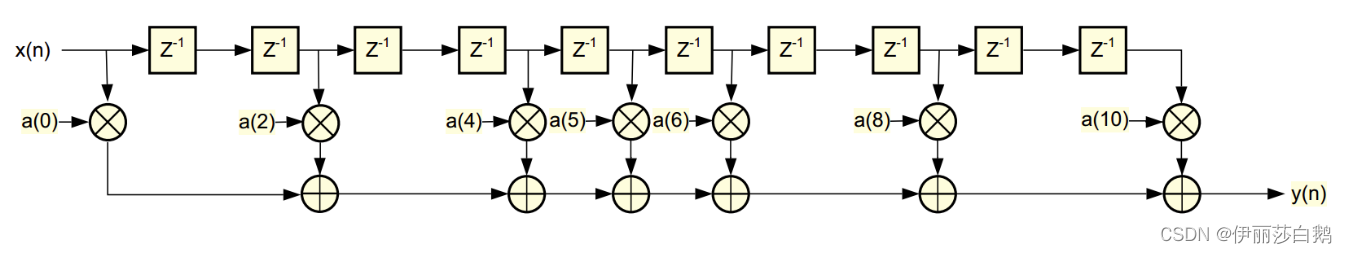

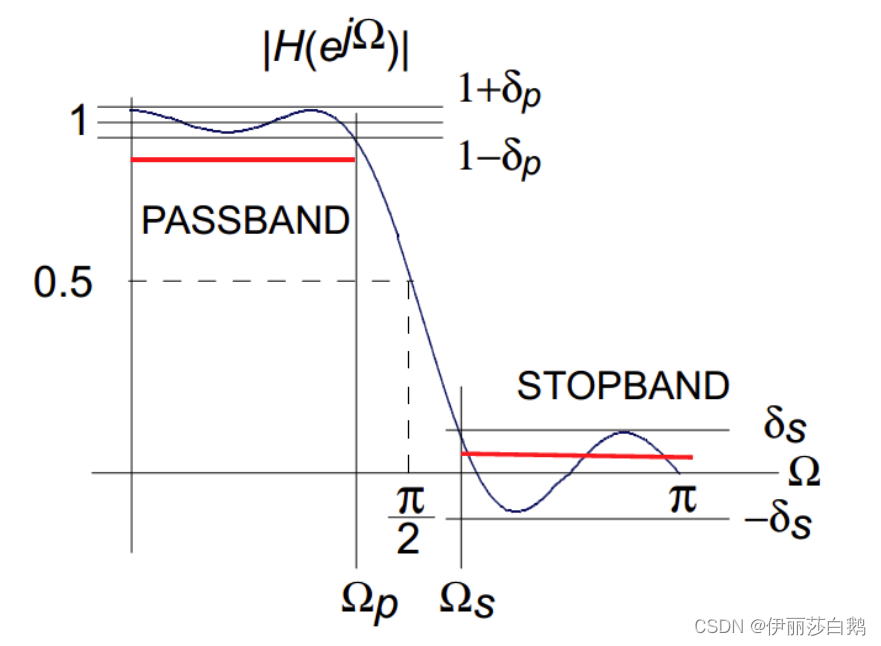

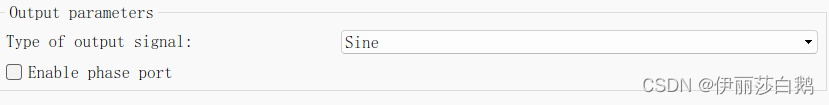

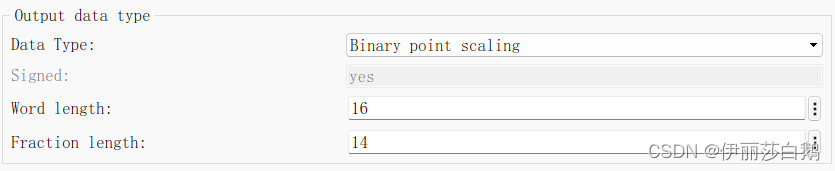

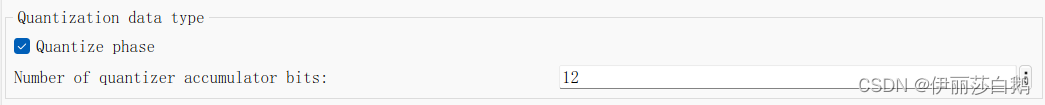

1.inc - Phase increment 相位增量 频率字可以选中外部输入或者内部设置 1.ouput data type 输出类型选择 2.phase 当前的相位输出 3.vaild 输出有效 输出可以是一个返回sin或cos值的端口,一个返回代表cos + j*sin的exp值的端口,或者两个返回sin和cos值的端口。 Matlab 手册提供的NCO的参考结构 3、 Quantized word length & Spurious Free Dynamic Range (SFDR dB) 设置滤波器系数结构,数据类型中设置定点化舍入方式已经系数和输出格式 实验使用半带滤波器做了多速率的实验 半带FIR,滤波器系数除了中间值为0.5外,其余偶数序号的系数都为0, 可以节约计算而且可以实现2倍抽取运算。这种滤波器由于通带和阻带相对于二分之一Nyquist频率对称,因而有近一半的滤波器系数精确为零。

|

【本文地址】

今日新闻 |

推荐新闻 |

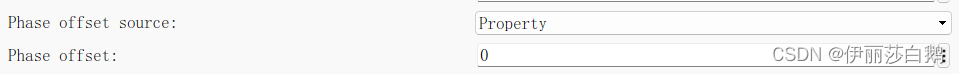

2.offset - Phase offset 相位偏移 相位偏移可以从外部输入或者内部输入

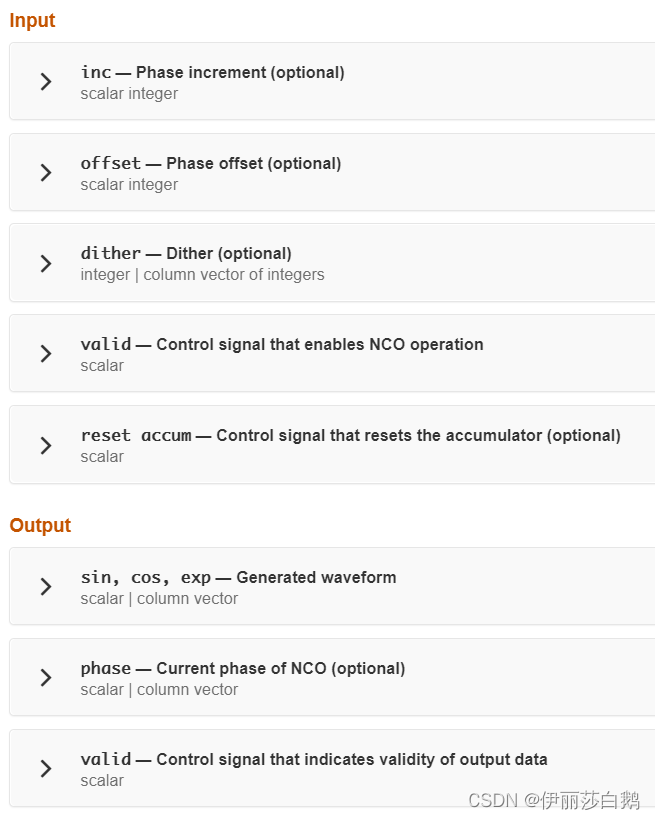

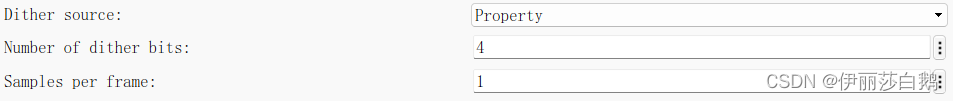

2.offset - Phase offset 相位偏移 相位偏移可以从外部输入或者内部输入  3.dither 动态杂散位数 SFDR,英文全称是 Spurious-Free Dynamic range,意为无杂散动态范围。SFDR是指基波强度与最大杂波或谐波的强度之比,所以SFDR值越大则说明系统的噪声水平越低,灵敏度越高。

3.dither 动态杂散位数 SFDR,英文全称是 Spurious-Free Dynamic range,意为无杂散动态范围。SFDR是指基波强度与最大杂波或谐波的强度之比,所以SFDR值越大则说明系统的噪声水平越低,灵敏度越高。  4.valid 输入有效 5.reset accum 复位模块

4.valid 输入有效 5.reset accum 复位模块

1、Accumulator word length — N NCO生成的频率依赖于增量的设置,在采样时间为

T

s

T_s

Ts,输出频率分辨率为

Δ

f

\Delta f

Δf 时

N

=

c

e

i

l

(

l

o

g

2

(

1

T

s

∗

Δ

f

)

)

N=ceil(log2(\frac{1}{T_s*\Delta f}))

N=ceil(log2(Ts∗Δf1))

1、Accumulator word length — N NCO生成的频率依赖于增量的设置,在采样时间为

T

s

T_s

Ts,输出频率分辨率为

Δ

f

\Delta f

Δf 时

N

=

c

e

i

l

(

l

o

g

2

(

1

T

s

∗

Δ

f

)

)

N=ceil(log2(\frac{1}{T_s*\Delta f}))

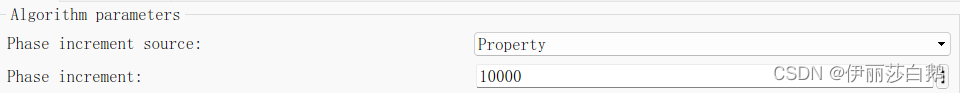

N=ceil(log2(Ts∗Δf1))  2、 Phase increment 相位增量 设

f

o

f_o

fo为需要输出的频率则频率字计算公式

p

h

a

s

e

i

n

c

r

e

m

e

n

t

=

r

o

u

n

d

(

f

o

T

s

2

N

)

~phase ~~increment=round(f_oT_s2^N)

phase increment=round(foTs2N)

2、 Phase increment 相位增量 设

f

o

f_o

fo为需要输出的频率则频率字计算公式

p

h

a

s

e

i

n

c

r

e

m

e

n

t

=

r

o

u

n

d

(

f

o

T

s

2

N

)

~phase ~~increment=round(f_oT_s2^N)

phase increment=round(foTs2N) Q

=

c

e

i

l

(

S

F

D

R

−

12

6

)

Q=ceil( \frac{SFDR-12}{6} )

Q=ceil(6SFDR−12)

Q

=

c

e

i

l

(

S

F

D

R

−

12

6

)

Q=ceil( \frac{SFDR-12}{6} )

Q=ceil(6SFDR−12)